**American Journal of Sciences and Engineering Research** E-ISSN -2348 – 703X, Volume 2, Issue 2, April - 2019

# A Fast FPGA based Architecture Implementation for Reversible Image Watermarking

## Kunal G

Department of Electronics Engineering, RKGIT. India.

**ABSTRACT:** Now a day's different techniques are available for digital image watermarking including software and hardware implementation. Reversible contrast mapping (RCM) is one of the technique is used for embed secret information into the digital form. RCM algorithm is simple integer transform of the pixel pair and there LSB bits are used for data embedding. RCM offers high embedding rate, low mathematical calculation and good robustness. This paper focuses on implementation of Field Programmable Gate Array (FPGA) based fast image watermarking using RCM algorithm. The given architecture requires 52 slices, 52 number of flip-flop, 85 number of 4-input LUTs and transceiver data rate is up to 3.2Gbps with an operating crystal frequency is 100MHz. Given architecture is implemented with Xilinx 14.7 on Spartan-6 FPGA family. The given architecture is acceptable for various application areas such as digital cameras, medical and military applications, etc.

Index Terms: Image Processing, RCM, FPGA

#### I. INTRODUCTION

Digital watermarking is a technique to embed secret information into the digital form is called watermarking. The main purpose is for copyright protection, security, etc. Reversible watermarking is used for lossless data compression and it provide authentication of the original image. And it has most of the used in medical, military applications. Different RW techniques proposed with different type of algorithm and most popular techniques are i) Difference Expansion, ii) Discrete Cosine transform ,iii) Discrete wavelet transform, iv) Histogram binshifting.[1]

However in this paper RCM-RW implemented technique is used, because of its low computational complexity and robustness. The goal of this proposed design is to achieve high speed hardware efficient VLSI architecture. The RCM algorithm was first implemented in Matlab to analyze the algorithm and various design parameters. After then desired architecture is established in FPGA (Spartan-6) using Xilinx.

#### II. PREVIOUS WORK

There are several software and hardware implementation algorithm are used a good number of research work is founded by in ICs and systems. Dinu coltue et al. [2] proposed very fast watermarking by RCM algorithm embedding information bit rate is high as compare to spatial Domain and this scheme does not need data compression. Mathematical calculation is also very complex. Gaurav Bhatnagar et al [3] via SVD method. The feasibility of this method and robustness of images with different attacks are tested by computer simulation. Ranganathan, N et al [4] implemented VLSI architecture for conventional watermarking using special domain algorithm. In hardware implementation inserted two image into original digital image using this technique. The IC chip with 0.35 µm technology implemented and consumes is 6.928mW. Mohanty et al. [5] another proposed watermarking technique into digital image using DCT domain. The IC chip with 0.35 µm technology and consume power is 62.78 mw. Maity et al. [6] specify New FWT based spared spectrum watermarking technique that can gives dual purpose verification in data transmission. Prototype design is used Xilinx Spartan-3 FPGA Board operating on 80MHZ frequency. P Karthigaikumar el at [7] proposed 'Implementation of robust watermarking processor with low power' this technique requires 457 number of slices with low power and it can implemented on ASIC and FPGA both also. Sugrev kaur et al [8] proposed a high speed low area FPGA implementation using DWT based image watermarking algorithm. It requires the 4708 slices and it work at 344MHZ frequency. Hirak maity et al. [9] proposed FPGA based VLSI architecture for digital image using RCM algorithm' They proposed two architecture of block size 8x8 and block size 32x32, architecture required 9881 slices, 11291 number of 4-input LUTs, 1.0395Mbps data rate and operating frequency 98.76MHz. Sudip Ghosh et al. [10] proposed another RCM algorithm for Reversible watermarking scheme based on FPGA. The architecture is encoder and decoder based design for faster implementation, encoder required 528 4-input LUTs and 303 slice and decoder required 613 LUTs 347 slices with max clock frequency of decoder is 45MHz.

#### III. RCM-RW ALGORITHM

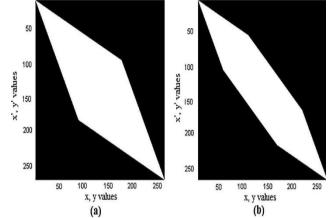

Let [0 L] be the gray image with image pixel intensity value between [0 255] Let [X,Y] be a pixel pair. The forward transform pixel pair is defined asX' = 2X-Y, Y'=2Y-X. The transform is to a sub domain DC $\subset$ 99[0, L] × [0, L] and it is noted as equations  $0 \le (2x - y) \le 255$  and  $0 \le (2y - x) \le 255$ . Dc coefficient is the rhombic shape with its diagonals [0, L] × [0, L] is shown in fig 1. [9].

Fig 1.Transform domain D (a) without DCcoefficient and (b) with DC coefficient.

#### A. Image Watermark embedding

In RCM algorithm the original image is partitioned into 8x8 image block. Then each image block is partition into pixels pair and watermark bit is embedded into LSBs of transform pixels pairs which is (X' Y') where X' indicates pixel pair is transformed or not and Y' indicate watermark inserting. The flow diagram of embedding watermark is shown in fig 2.

Fig 2 The Flow diagram of watermark embedding

#### B. Image Watermark extraction

Inverse transform is applied for watermark extraction. Watermarked image is again partitioned into 8x8 image block and pixel pair then checks two object conditions. The process is repeated again and again until covers all pixel pairs. The flow diagram of image extraction watermark is shown in fig 3.

#### IV. VLSI ARCHTECTURE OF RCM

Implementation of the watermarking algorithm is done using the ISE Design suite of Xilinx 14.7 for Spartan 6FPGA family. FPGA because of its advantages like Reconfigurability, low cost, high speed & simpler design process is used for hardware implementation. Security level offered by the hardware based watermarking techniques is higher than the software based watermarking techniques. Watermark embedding and watermark extraction of original image is done through the RCM algorithm.

#### V. PROTOTYPE DESIGN OF FPGA

This design unit consist the two main parts one is watermark embedding and other is watermark extraction. Each part have separate functional block, Mux, address decoder, flip-flop, memory shift register etc. These blocks are tested and verified through Xilinx simulation. Once all parts are tested and verified, the different modules are connected in series together according to controller instructions.

**A. FPGA architecture for image watermark embedding part** In watermark embedding part consist image partitioning unit, comparator unit memory unit. The original image and watermark image are received and stored in SBUF. Then original image with size 8x8 and watermark image with size 8x8 blocks are converted into the integer form (bits). Watermark embedding process is done, this is compression technique again the integer form is converted into (8x8) image block set and transmitted to PC. Experimental results are obtained on Matlab, For the data reading and writing purpose clock signal is required, here address decoder is used for generate clock. The block diagram of hardware architecture for image watermark embedding part is shown in fig 4.

#### VI. EXPERIMENTAL RESULTS AND DISCUSSIONS

The proposed technique is tested and verified on different images. Original image (Lena) with size 128x128 and watermark image (Beam) with size 64x64 applied proposed algorithm on this images and resulted watermarked image (embedding) is shown in fig 10. Again apply the inverse transform of the proposed algorithm extracted image is shown in fig 11. Proposed scheme is evaluated using objective parameters such as Peak Signal to noise ratio (PSNR), Mean square error (MSE) and structural similarity index measure (SSIM) for checked quality of image. Watermarked image is obtained after embedding bit rate is 0.45bpp.

#### VII. CONCLUSION

This paper focuses on a fast FPGA based image watermarking using RCM algorithm. Because of its low computational complexity, simplicity and easily implemented on hardware. Implementation on hardware is very simple, fast and it required less number resources only 52 no. of slices, 52 no. of flip flops and 85 4-input LUTs and transceiver data rate up to 3.2Gbps with operating 100MHz crystal frequency. The proposed architecture is acceptable for various application areas such as digital cameras, medical and military applications, etc.

#### REFERENCES

- 1. Gaurav Bhatnagar, Q.M. Jonathan Wu, Balasubramanian Raman," A new robust adjustable logo watermarking scheme" ScienceDirect 2012 pp. 40-58.

- Mohanty, S.P., Ranganathan, N., Namballa, R.K, "VLSI implementation of visible watermarking for a secure digital still camera design" In: Proceedings of the 17<sup>th</sup> International Conference on VLSI Design, 2004, pp. 1063-1068.

- 3. Mohanty, S.P., Ranganathan, N., Balakrishnan, K., A dual voltage frequencyVLSI chip for image watermarking in DCT domain. IEEE Trans. Circuits Syst. II:Exp. Briefs 53 (May (5)),pp. 394–398.

- Maity, S.P., Kundu, M., Maity, S., 2009. Dual purpose FWT domain spread spectrumimage watermarking in real time, special issue on circuits and systems for realtime security and copyright protection of multimedia. Int. J. Comput. Electr. Eng.35, 415–433.

- 5. P Karthigaikumar, K Baskaran, "An ASIC implementation of a low power invisible robust watermarking processor" International journal of system architecture, 2010, 57(4), 404-411.

- 6. Sugreev Kaur And Rajesh Mehra, "High Speed And Area Efficient 2D DWT Processor Based Image

### American Journal Of Sciences And Engineering Research iarjournals.com

Compression" Signal & Image Processing : An International Journal Sipij, 2010, 1(2), pp.22-31.

- 7. Hirak Kumar Maitya, Santi P. Maity, "FPGA implementation of reversible watermarking in digital images using reversible contrast mapping" Science Direct June 2014.

- 8. Sudip Ghosh, Bijoy Kundu, Debopam Datta, Santi P Maity and Hafizur Rahaman, "Design and Implementation of Fast FPGA Based Architecture for Reversible Watermarking", International Conference on Electrical Information and Communication Technology, 1-6, IEEE 2013